# Device-Level Majority von Neumann Multiplexing

#### Valeriu Beiu

United Arab Emirates University, UAE

#### **Walid Ibrahim**

United Arab Emirates University, UAE

#### Sanja Lazarova-Molnar

United Arab Emirates University, UAE

### INTRODUCTION

This chapter starts from an exact gate-level reliability analysis of von Neumann multiplexing using majority gates of increasing fan-ins ( $\Delta = 3, 5, 7, 9, 11$ ) at the smallest redundancy factors ( $R_E = 2\Delta$ ), and details an accurate device-level analysis. The analysis complements well-known theoretical and simulation results. The gate-level analysis is exact as obtained using exhaustive counting. The extension (of the exact gate-level analysis) to device-level errors will allow us to analyze von Neumann majority multiplexing with respect to device malfunctions. These results explain abnormal behaviors of von Neumann multiplexing reported based on Monte Carlo simulations. These analyses show that device-level reliability results are quite different from the gate-level ones, and could have profound implications for future (nano)circuit designs.

SIA(2005) predicts that the semiconductor industry will continue its success in scaling CMOS for a few more generations. This scaling should become very difficult when approaching 16 nm. Scaling might continue further, but alternative nanodevices might be integrated with CMOS on the same platform. Besides the higher sensitivities of future ultra-small devices, the simultaneous increase of their numbers will create the ripe conditions for an inflection point in the way we deal with reliability.

With geometries shrinking the available reliability margins of the future nano(devices) are considerably being reduced (Constantinescu, 2003), (Beiu et al., 2004). From the chip designers' perspective, reliability currently manifests itself as time-dependent uncertainties and variations of electrical parameters. In the nano-era, these device-level parametric uncertainties

are becoming too high to handle with prevailing worst-case design techniques—without incurring significant penalty in terms of area, delay, and power/energy. The global picture is that reliability looks like one of the greatest threats to the design of future ICs. For emerging nanodevices and their associated interconnects the anticipated probabilities of failures, could make future nano-ICs prohibitively unreliable. The present design approach based on the conventional zero-defect foundation is seriously being challenged. Therefore, fault- and defect-tolerance techniques will have to be considered from the early design phases.

Reliability for beyond CMOS technologies (Hutchby et al., 2002) (Waser, 2005) is expected to get even worse, as device failure rates are predicted to be as high as 10% for single electron technology, or SET (Likharev, 1999), going up to 30% for self-assembled DNA (Feldkamp & Niemeyer, 2006) (Lin et al., 2006). Additionally, a comprehensive analysis of carbon nano tubes for future interconnects (Massoud & Nieuwoudt, 2006) estimated the variations in delay at about 60% from the nominal value. Recently, defect rates of 60% were reported for a 160 Kbit molecular electronic memory (Green et al., 2007). Achieving 100% correctness with 10<sup>12</sup> nanodevices will be not only outrageously expensive, but plainly impossible! Relaxing the requirement of 100% correctness should reduce manufacturing, verification, and test costs, while leading to more transient and permanent errors. It follows that most (if not all) of these errors will have to be compensated by architectural techniques (Nikolić et al., 2001) (Constantinescu, 2003) (Beiu et al., 2004) (Beiu & Rückert, 2009).

From the system design perspective errors fall into: *permanent* (defects), *intermittent*, and *transient*

(faults). The origins of these errors can be found in the manufacturing process, the physical changes appearing during operation, as well as sensitivity to internal and external noises and variations. It is not clear if emerging nanotechnologies will not require new fault models, or if multiple errors might have to be dealt with. Kuo (2006) even mentioned that: "we are unsure as to whether much of the knowledge that is based on past technologies is still valid for reliability analysis." The well-known approach for fighting against errors is to incorporate redundancy: either static (in space, time, or information) or *dynamic* (requiring fault detection, location, containment, and recovery). Space (hardware) redundancy relies on voters (generic, inexact, midvalue, median, weighted average, analog, hybrid, etc.) and includes: modular redundancy, cascaded modular redundancy, and multiplexing like von Neumann multiplexing vN-MUX (von Neumann, 1952), enhanced vN-MUX (Roy & Beiu, 2004), and parallel restitution (Sadek et al., 2004). Time redundancy is trading space for time, while information redundancy is based on error detection and error correction codes.

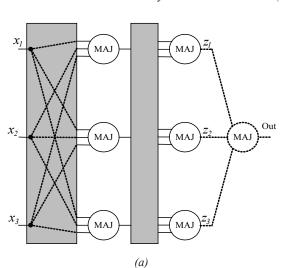

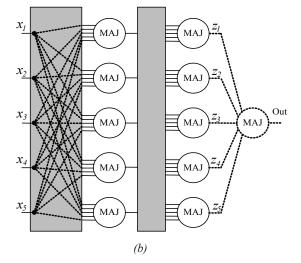

This chapter explores the performance of vN-MUX when using majority gates of fan-in  $\Delta$  (MAJ- $\Delta$ ). The aim is to get a clear understanding of the trade-offs between the reliability enhancements obtained when using MAJ- $\Delta$  vN-MUX at the smallest redundancy factors  $R_F = 2\Delta$  (see Fig. 1) on one side, versus both the fan-ins and the unreliable nanodevices on the other side. We shall start by reviewing some theoretical and simulation results for vN-MUX in Background section.

Exact gate-level simulations (as based on an exhaustive counting algorithm) and accurate device-level estimates, including details of the effects played by nanodevices on MAJ- $\Delta$  vN-MUX, are introduced in the Main Focus of the Chapter section. Finally, implications and future trends are discussed in Future Trends, and conclusions and further directions of research are ending this chapter.

### **BACKGROUND**

Multiplexing was introduced by von Neumann as a scheme for reliable computations (von Neumann, 1952). vN-MUX is based on successive computing stages alternating with random interconnection stages. Each computing stage contains a set of redundant gates. Although vN-MUX was originally exemplified for NAND-2 it can be implemented using any type of gate, and could be applied to any level of abstraction (subcircuits, gates, or devices). The 'multiplexing' of each computation tries to reduce the likelihood of errors propagating further, by selecting the more-likely result(s) at each stage. Redundancy is quantified by a redundancy factor  $R_{E}$ , which indicates the multiplicative increase in the number of gates (subcircuits, or devices). In his original study, von Neumann (1952) assumed independent (un-correlated) gate failures  $pf_{GATE}$  and very large  $R_F$ . The performance of NAND-2 vN-MUX was compared with other fault-tolerant techniques in (Forshaw et al., 2001), and it was analyzed at lower

Figure 1. Minimum redundancy MAJ- $\Delta$  vN-MUX: (a) MAJ-3 ( $R_E = 6$ ); and (b) MAJ-5 ( $R_E = 10$ )

7 more pages are available in the full version of this document, which may be purchased using the "Add to Cart" button on the publisher's webpage: <a href="www.igi-global.com/chapter/device-level-majority-von-neumann/10289">www.igi-global.com/chapter/device-level-majority-von-neumann/10289</a>

### Related Content

### Finding Multiple Solutions with GA in Multimodal Problems

Marcos Gestaland Mari Paz Gómez-Carracedo (2009). *Encyclopedia of Artificial Intelligence (pp. 647-653)*. www.irma-international.org/chapter/finding-multiple-solutions-multimodal-problems/10315

# Noise Resistant Morphological Algorithm of Moving Forklift Truck Detection on Noisy Image Data

Vladimir Olegovich Chernousovand Andrey Vladimirovich Savchenko (2014). *International Journal of Conceptual Structures and Smart Applications (pp. 36-54).*

www.irma-international.org/article/noise-resistant-morphological-algorithm-of-moving-forklift-truck-detection-on-noisy-image-data/134887

## Intelligent Decision Making and Risk Analysis of B2c E-Commerce Customer Satisfaction

Masoud Mohammadian (2015). *International Journal of Fuzzy System Applications (pp. 60-75).* www.irma-international.org/article/intelligent-decision-making-and-risk-analysis-of-b2c-e-commerce-customersatisfaction/126199

# Optimizing the Performance of Plastic Injection Molding Using Weighted Additive Model in Goal Programming

Abbas Al-Refaieand Ming-Hsien Li (2011). *International Journal of Fuzzy System Applications (pp. 43-54)*. www.irma-international.org/article/optimizing-performance-plastic-injection-molding/54241

#### PCA as Dimensionality Reduction for Large-Scale Image Retrieval Systems

Mohammed Amin Belarbi, Saïd Mahmoudiand Ghalem Belalem (2017). *International Journal of Ambient Computing and Intelligence (pp. 45-58).*

www.irma-international.org/article/pca-as-dimensionality-reduction-for-large-scale-image-retrieval-systems/187067